在FPGA上设计和实现带集成7段显示器的3位ALU

原标题:Design and Implementation of a 3-bit ALU with Integrated 7-Segment Display on FPGA

5 分

关键词

摘要

本文描述了一个3位算术逻辑单元(ALU)的设计和实现,该单元集成了7段显示器输出,并部署在FPGA平台上。该项目的目标是通过基于FPGA的ALU高效地执行和显示基本的算术和逻辑运算,包括加法、减法、与、或、异或和非运算。一个控制信号选择操作,ALU的3位结果被解码并显示在7段接口上,以便清晰地输出可视化。ALU设计使用Verilog编码,并包括管理算术功能中的进位和溢出的逻辑。显示解码器模块将ALU的二进制输出映射到7段显示器上的正确LED段,允许直观地实时读取操作结果。该系统在Artix-7 FPGA上使用Xilinx Vivado开发环境进行了综合、仿真和测试,在所有操作中实现了准确和预期的功能。该工作展示了FPGA技术在将计算和显示集成到紧凑数字系统中的有效性,具有在实时处理和显示至关重要的教育和嵌入式系统设计环境中的潜在应用。关键词:FPGA,ALU,7段显示器,Verilog,数字系统设计,嵌入式计算。

AI理解论文

该文档是一篇关于3位算术逻辑单元(ALU)设计与实现的论文,集成了7段显示器,并部署在**FPGA(现场可编程门阵列)**平台上。以下是对该论文的详细总结:

1. 引言

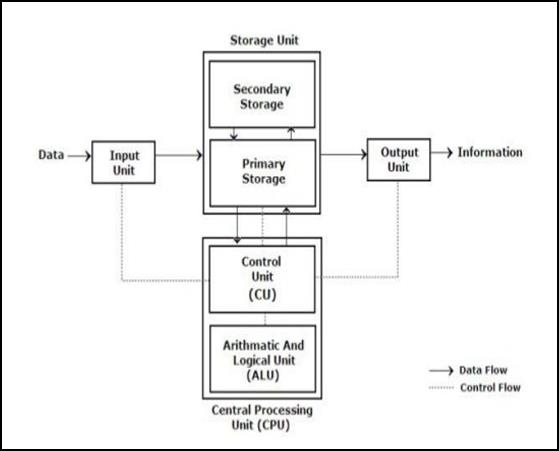

论文首先介绍了**算术逻辑单元(ALU)**在数字系统中的重要性,ALU负责执行关键的算术和逻辑操作,是处理器和嵌入式系统的基础。随着对灵活高效数字电路的需求增加,FPGA因其高速处理、可重构性和无缝集成潜力而越来越受到青睐。本文的目标是设计一个能够执行加法、减法、与、或、异或和非等操作的3位ALU,并在集成的7段显示器上实时显示结果。

2. 文献综述

文献综述部分指出,FPGA平台提供了实现和定制ALU设计的灵活性,7段显示器的集成增强了用户交互,提供了一种直观的结果显示方法。相关研究为高效可扩展的ALU设计提供了基础,这些设计可以与显示系统无缝集成,具有重要的实际应用潜力。

3. 设计系统

3.1 顶层设计

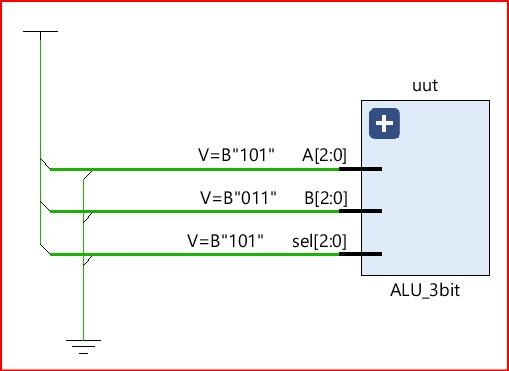

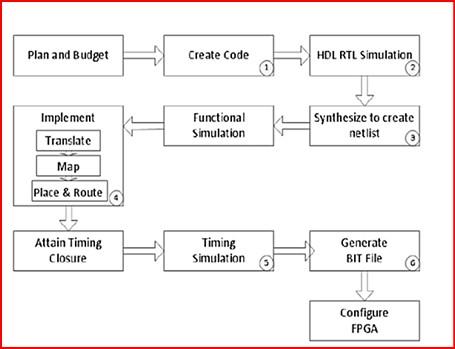

论文描述了顶层(RTL)Verilog模块的设计,RTL设计明确规定了所有寄存器及其之间的组合逻辑。使用高层次设计方法可以简化复杂系统的描述和评估,加快设计过程。

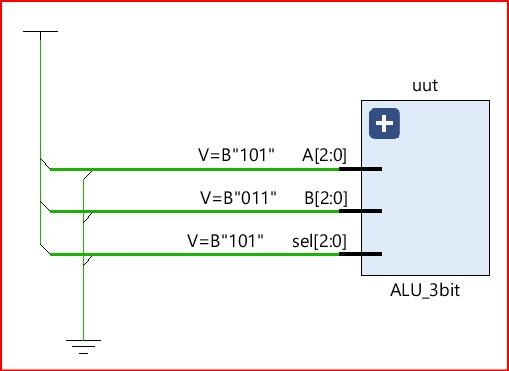

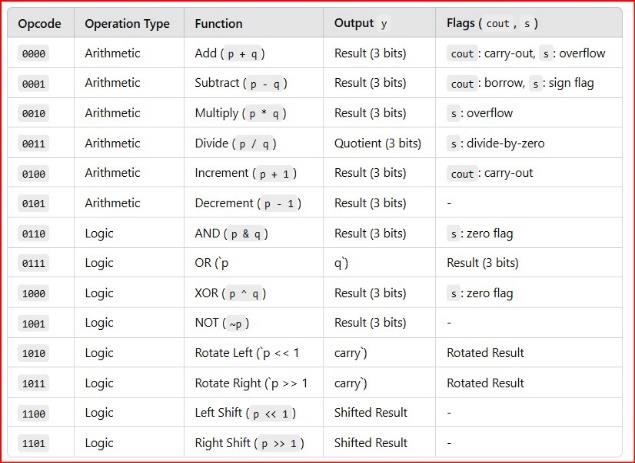

3.2 ALU功能

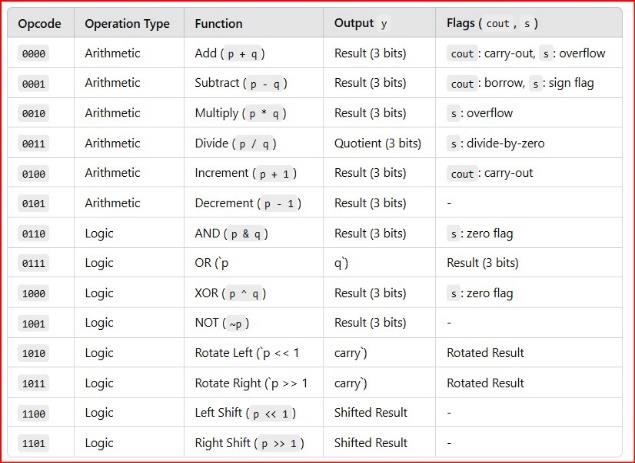

3位ALU通过将功能划分为算术单元和逻辑单元来执行操作。算术单元处理加法、减法、乘法、除法、递增和递减等计算,生成3位结果,并提供进位和状态标志。逻辑单元管理按位操作,如与、或、异或、非、左旋转、右旋转、左移位和右移位。操作由4位控制信号选择,输出包括3位结果和附加标志。

4. 实现过程

论文详细描述了在Artix-7 FPGA上的实现过程,包括合成、实现、生成比特流文件以及硬件编程和测试。Artix-7 FPGA因其低功耗和成本敏感应用而被选用,适合高性能、低功耗应用。

5. 结果与讨论

5.1 RTL原理图

RTL原理图提供了架构的蓝图,确保设计符合规范。使用Verilog将架构描述转换为功能表示。

5.2 技术原理图

技术原理图以查找表(LUTs)的形式表示架构,LUT是估算VLSI架构设计中使用面积的关键参数。

5.3 仿真

仿真报告记录了仿真过程的结果,验证了设计的功能。仿真确认了ALU的正确功能,输出和标志行为与预期结果一致。

6. 结论

论文总结了3位ALU在Artix-7 FPGA上的设计与实现,成功执行了预期功能。ALU准确执行了一系列算术和逻辑操作,结果在7段显示器上可靠显示,进位和零标志得到适当指示。该项目展示了基于FPGA设计的高效高性能数字系统实现能力,为未来扩展和更复杂设计提供了坚实框架。

7. 致谢

作者感谢电子与通信工程系的支持和指导,特别是指导教师在项目各阶段提供的建议和指导。

8. 未来展望

未来,该项目可以通过支持更宽的位宽(如8位或16位)来扩展ALU的功能,并集成更高级的操作如乘法、除法和逻辑移位。设计还可以通过利用Artix-7 FPGA的高级特性进行优化,以提高功率效率和速度。此外,ALU可以集成到更大的数字系统中,用于实时处理应用。

术语解释

- FPGA(现场可编程门阵列):一种集成电路,用户可以在现场通过硬件描述语言(如Verilog)进行编程。

- Verilog:一种硬件描述语言,用于描述电子系统的结构和行为。

- RTL(寄存器传输级):一种设计抽象级别,描述了寄存器和它们之间的组合逻辑。

- LUT(查找表):FPGA中用于实现逻辑函数的基本单元。

通过以上总结,读者可以全面理解该论文的内容、方法和贡献。